擁抱創新,洞察汽車前沿技術與突破——2025上海車展電氣科技側記

2025年的上海車展,在黃浦江畔再次成為全球汽車工業矚目的焦點。本屆車展以“智行·凈界”為主題,不僅展示了設計美學與出行理念的革新,更成為電氣科技領域內一次技術開發的集中檢閱與前瞻洞察。從核心三電系統的突破到智能能源生態的構建,創新浪潮正以前所未有的深度與廣度,重塑著汽車的形態與未來。

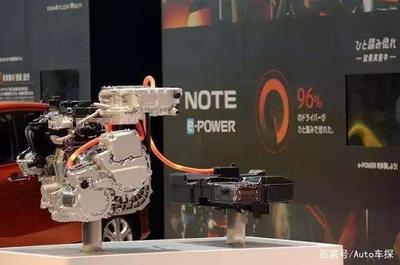

走進展館,首先感受到的是電驅動系統的高效化與集成化趨勢。多家車企推出了新一代“八合一”超集成電驅系統,將電機、電控、減速器、車載充電機、直流變換器、配電模塊等關鍵部件高度整合,體積較上一代減少30%,重量降低25%,而綜合效率卻提升至驚人的97%。這意味著更長的續航、更緊湊的布局與更低的能耗,標志著電驅動總成技術已從“堆料”階段邁入“精工”時代。固態電池技術終于從實驗室走向量產前夜。數家頭部企業展出了能量密度超過400Wh/kg的準固態電池樣品,并宣布將在2026-2027年實現裝車。其更安全、更耐低溫的特性,有望徹底解決當前液態鋰離子電池的里程焦慮與安全隱憂,成為下一代電動汽車的“心臟”。

充電補能體系的革新同樣引人注目。800V高壓快充平臺已成為中高端新車的“標配”,配合新一代碳化硅功率器件,可實現“充電10分鐘,續航400公里”的體驗。更令人矚目的是,無線充電技術開始步入商業化示范階段。地面埋設的發射線圈與車輛接收裝置,在精準對位后即可實現高效率的能量傳輸,為未來自動駕駛車輛的自動補能提供了優雅的解決方案。車展現場設置的動態無線充電演示路段,讓觀眾親眼目睹了“行駛中充電”的可能。

智能,是電氣化的高階延伸。本次車展清晰地展現了“電驅”與“智算”的深度融合。基于中央集中式電子電氣架構的新車型,將整車控制、智能駕駛、智能座艙的功能集成于少數幾個高性能計算平臺(HPC)。這不僅簡化了線束,更實現了能量的全局智能管理。車輛能根據實時路況、駕駛習慣、電池狀態,動態調整各系統的功耗分配,甚至提前預判能耗,規劃最高效的行駛與充電策略,讓每一度電都發揮最大價值。

車輛與電網(V2G)的雙向互動技術開始落地。多款新車具備了向電網反向輸電的能力,在用電低谷時充電儲能,在高峰時向電網送電,既為用戶創造收益,也助力電網削峰填谷,使電動汽車成為移動的儲能單元,融入更宏大的智慧能源網絡。

2025上海車展如同一扇窗口,讓我們清晰地看到,汽車電氣科技的技術開發已超越單純的動力替換,正朝著更高效率、更強智能、更廣生態協同的方向縱深突破。這是一場涉及材料科學、電力電子、軟件算法、能源管理的系統性創新競賽。擁抱這些創新,不僅是在選擇一種交通工具,更是在參與構建一個更清潔、更高效、更互聯的可持續出行未來。前沿技術正加速突破實驗室的壁壘,駛入我們的生活,而上海車展,正是這場偉大變革的最佳見證與起點。

如若轉載,請注明出處:http://www.3avl80.cn/product/50.html

更新時間:2026-04-05 09:36:34