新春走基層 聽見產業升級的“向新力”——電氣科技領域技術開發一線觀察

新春伊始,萬象更新。走進位于長三角的一家電氣科技企業研發中心,這里沒有節日的閑適,只有鍵盤敲擊聲、設備運行聲與工程師們熱烈討論聲交織成的獨特“春曲”。這聲音背后,是中國產業升級浪潮中,電氣科技領域澎湃的“向新力”——一股向著新技術、新應用、新未來全力進發的創新力量。

一、實驗室里的“突破聲”:從跟跑到并跑

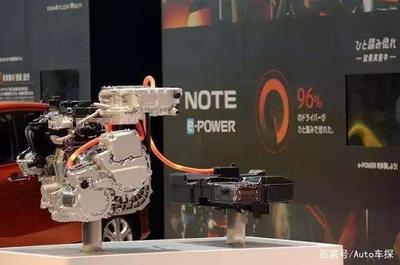

在高壓電氣設備實驗室,一臺新型環保氣體絕緣開關設備正在進行最后的耐久性測試。項目負責人李工介紹:“傳統的六氟化硫氣體絕緣性能雖好,但溫室效應潛能值極高。我們歷時三年攻關,終于找到了性能相當且幾乎零排放的替代混合氣體與絕緣結構。”他指著屏幕上跳動的數據,語氣中充滿自豪:“這項突破,讓我們在環保電氣裝備賽道,從過去的‘跟跑’實現了關鍵領域的‘并跑’,甚至局部‘領跑’。” 實驗室里,類似這樣的“突破聲”不絕于耳。在功率半導體模塊研發線上,團隊正致力于提升第三代半導體碳化硅器件的可靠性與成本控制,旨在為新能源汽車、光伏逆變提供更高效的“心臟”;在智能傳感團隊,微型化、高精度的在線監測裝置不斷迭代,讓龐大電網的“脈搏”與“體溫”盡在掌握。這些聲音,共同譜寫著電氣技術從基礎材料、核心部件到系統集成全方位創新的主旋律。

二、生產線上的“協奏曲”:智能化賦能制造升級

離開實驗室,步入智能生產車間,又是另一番景象。機械臂精準地裝配著精密零件,AGV小車沿著既定路線無聲穿梭運送物料,中央控制室的大屏實時可視化呈現著生產全流程數據。“聽得見”的是設備高效運轉的韻律,“聽得懂”的是數據流背后智能決策的“心跳”。車間王主任表示:“我們打造的這條數字化柔性生產線,可快速響應小批量、多品種的高端定制訂單。通過工業互聯網平臺,研發端的最新成果能以最快速度轉化為穩定產能。” 產業升級的“向新力”,不僅體現在尖端技術的突破,也深深融入制造模式的革新。智能化改造大幅提升了產品質量的一致性與生產效率,降低了能耗與成本,讓“中國制造”在電氣高端裝備領域更具競爭力。一線工人也從重復勞動中解放出來,轉變為設備的“指揮官”與“醫生”,他們的討論焦點更多集中在工藝優化與異常排查上——這是產業升級中人力資本提升的生動注腳。

三、應用現場的“回響”:技術落地驅動綠色轉型

技術的價值在于應用。跟隨工程師的腳步,我們來到一個新建的海上風電升壓站。這里采用了企業最新研發的緊湊型、耐腐蝕、高可靠的電氣成套設備。“面對海上嚴苛環境與運維高成本,設備必須極度可靠、免維護周期長。”現場服務的趙工頂著海風說,“我們的技術在這里經受考驗,也在支撐著清潔能源的穩定送出。” 從特高壓輸電到分布式智能電網,從電動汽車充電網絡到工業園區的綜合能源管理,電氣新技術的“回響”正在國民經濟各個角落激蕩。它們不僅是產業升級的成果,更成為驅動能源革命、實現“雙碳”目標的關鍵力量。用戶的需求反饋、現場的應用挑戰,又源源不斷地傳回研發端,激發著新一輪的創新循環。

****

這個春天,在電氣科技領域的基層一線,我們聽見了鉆研突破的執著之聲、智能制造的協同之聲、綠色應用的澎湃之聲。這些聲音匯聚成的“向新力”,堅實而有力。它源自無數科研人員與工程師的埋頭苦干,得益于產學研用的緊密耦合,更彰顯了中國產業向著全球價值鏈中高端邁進的堅定決心。這股力量,正持續為高質量發展注入強勁動能,照亮新型工業化的未來之路。

如若轉載,請注明出處:http://www.3avl80.cn/product/53.html

更新時間:2026-04-05 20:12:43